Signetik 2650 - Signetics 2650

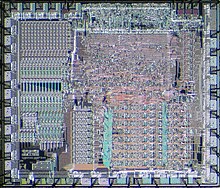

Signetics 2650AN

| |

| Allgemeine Information | |

|---|---|

| Gestartet | 1975 |

| Gängige Hersteller | |

| Leistung | |

| max. CPU- Taktrate | 1,2 MHz |

| Datenbreite | 8 |

| Adressbreite | fünfzehn |

| Physikalische Spezifikationen | |

| Pakete) | |

Der Signetics 2650 war ein 8-Bit- Mikroprozessor , der im Juli 1975 eingeführt wurde. Laut Adam Osbornes Buch An Introduction to Microprocessors Vol 2: Some Real Products war er "der Minicomputer- ähnlichste" der damals erhältlichen Mikroprozessoren. Eine Kombination aus fehlenden Funktionen und seltsamem Speicherzugriff schränkte seine Attraktivität ein, und das System wurde auf dem Markt wenig verwendet. Signetics wurde als Second-Source-Lieferant für den MOS 6502 bekannter .

Geschichte

1972 stellte Jack Curtis von Signetics John Kessler von IBM ein , um das Design einer neuen Single-Chip-CPU zu leiten, die mit Minicomputersystemen konkurrieren sollte . Als Vorbild für das neue Design wählte Kessler den IBM 1130 . Der 1965 veröffentlichte 1130 war ein 16-Bit- Minicomputer , der viele Designmerkmale mit anderen Minis dieser Ära teilte.

Während Kessler die Architektur entwarf, entwarf Kent Andreas die CPU unter Verwendung eines kürzlich entwickelten Ionenimplantations- NMOS- Prozesses. Im Gegensatz zu dem weit verbreiteteren PMOS- Prozess der Ära verbrauchte NMOS weniger Strom und leitete weniger Wärme ab. Dadurch konnte der Chip mit höheren Geschwindigkeiten betrieben werden als PMOS-CPU-Designs, und die ersten 2650er liefen mit der gleichen Geschwindigkeit von 1,25 MHz wie die zeitgenössischen Modelle der 1130.

Als er 1972 entwickelt wurde, gehörte der 2650 zu den fortschrittlichsten Designs auf dem Markt und übertraf die Intel 4004 und 8008 der gleichen Ära bei weitem . Trotzdem wurde das Design nicht zur Produktion freigegeben. Zu dieser Zeit war Signetics stark an Dolby Laboratories beteiligt und entwickelte integrierte Schaltkreise , die Dolbys Suite von Rauschunterdrückungssystemen implementierten . Die Produktion des 2650 wurde zurückgestellt und die CPU wurde erst im Juli 1975 offiziell eingeführt. Bis 1975 wurden mehrere neue CPUs eingeführt, die von Anfang an als 8-Bit-Maschinen konzipiert waren, anstatt ein älteres Design nachzuahmen, und die Vorteile der 2650 waren nicht mehr so überzeugend.

1975 kaufte Philips Signetics, und ab diesem Zeitpunkt sind Versionen des 2650 sowohl mit Signetics- als auch mit Philips-Markenzeichen erhältlich.

Im März 1976 schloss Signetics eine Second-Source-Vereinbarung mit Advanced Memory Systems (AMS). Zu dieser Zeit waren die meisten CPU-Firmen sehr klein und niemand kaufte ein Design von einer Firma, die in Konkurs gehen könnte. Second-Sourcing war ein wichtiger Garant dafür, dass das Design auch in diesem Fall verfügbar bleibt. AMS fungierte bereits als Second Source für den RCA 1802 , ein fortschrittliches CMOS- Design, und der NMOS 2650 wurde als nützliche Ergänzung angesehen, die nicht direkt mit dem 1802 konkurrieren würde. Leider wurde AMS im November von Intersil gekauft , die ihre eigene Intersil 6100 , eine Single-Chip-Version des PDP-8 mini. Intersil hat die Produktion des 2650 eingestellt.

Signetics versuchte es 1977 erneut mit National Semiconductor , die im letzten Quartal des Jahres Versionen einführen wollten. Aus unbekannten Gründen scheint dies nie passiert zu sein, und es wurde nur ein einziges Beispiel einer NS-Version aus Frankreich gefunden.

Signetics setzte die Entwicklung des 2650 fort und führte 1977 zwei neue Modelle ein. Der 2650A war eine überarbeitete Version des ursprünglichen Layouts, um den Ertrag zu verbessern und damit die Kosten zu senken. Die Geschwindigkeit blieb unverändert bei 1,25 MHz für das Basismodell und 2 MHz für die -1 Versionen. Der 2650B basierte auf dem A, fügte eine Reihe neuer Befehle hinzu und verbesserte die Leistung einer Reihe vorhandener Befehle.

Beschreibung

Das Gesamtdesign des 2650 basierte auf dem IBM 1130 . Daher verfügt der 2650 über eine Reihe von Funktionen, die bei Minicomputern der 1960er Jahre üblich waren , aber bei neu entwickelten Mikroprozessoren der 1970er Jahre selten zu finden sind. Darunter befanden sich zum Beispiel Statusbits, die verwendet wurden, um den Status von Eingabe-/Ausgabegeräten zu verfolgen , was das Schreiben von Schnittstellencode vereinfacht. Ein weiteres Mini-ähnliches Feature war die Verwendung von vektorisierten Interrupts , die es Geräten ermöglichten, den richtigen Interrupt-Handler- Code aufzurufen, indem sie ihren Speicherort auf den Datenbus legten und dann einen Interrupt erzwangen. Dies vermeidet die Notwendigkeit, einen zentralisierten Interrupt-Handler zu schreiben, der zusätzliche Daten vom Bus liest, bestimmt, welcher Gerätetreiber aufgerufen wird, und ihn dann aufruft; der 2650 kann direkt zum richtigen Code springen, der möglicherweise auf dem Gerät selbst gespeichert ist.

Wie beim 1130 waren die Prozessorregister des 2650 in Sätze unterteilt, wobei ein einziges globales Register R0 als Akkumulator verwendet wurde , und zwei Sätze von Indexregistern , beide mit den Namen R1, R2 und R3, also insgesamt sieben Registern. Zu jedem Zeitpunkt war einer der beiden Indexsätze für die CPU sichtbar. Welche Menge sichtbar war, wurde durch ein Bit im Statusregister PSW gesteuert . Man könnte leicht mit einem einzigen Befehl zwischen den beiden Registersätzen umschalten. Dies ermöglichte ein schnelles Umschalten von Werten während Unterprogrammaufrufen, Betriebssystemwechseln oder der Behandlung von Interrupts. Im Gegensatz zum 1130 waren die Register nur 8 Bit breit und nicht 16 Bit, und es gab nur zwei Sätze anstelle der drei beim 1130.

Ein weiteres Mini-ähnliches Merkmal war die umfassende Unterstützung der indirekten Adressierung bei den meisten Befehlen. Viele Befehle erfordern das Lesen von Daten von einer Stelle im Speicher, in den meisten CPUs der Ära wäre dies ein einzelnes Datenbyte, das im Speicher gespeichert ist, auf den eine 16-Bit-Stelle Bezug nimmt. Beim 2650 zeigte das High-Bit dieser 16-Bit-Stelle Indirektion an, was bedeutet, dass sich die Daten nicht an dieser Stelle im Speicher befanden, sondern in den verbleibenden 15 Bits der Adresse kodiert. Diese Art des Zugriffs ermöglichte einen leichteren Zugriff auf Datenblöcke als in Systemen, die eine Umleitung ausschließlich durch spezielle Befehle oder ausschließlich durch Indexregister ermöglichten. Man konnte durch den Speicher blättern, indem man den im Speicher gespeicherten Adresswert inkrementiert. Dies führte auch dazu, dass eine beträchtliche Anzahl von mathematischen Anweisungen auf Adressen angewendet wurde, und um die Leistung dieser Operationen zu verbessern, enthielt der 2650 eine zweite arithmetische Logikeinheit nur für Adressberechnungen.

Der Nachteil dieses Ansatzes war, dass das High-Bit nicht mehr Teil der Adresse war, was bedeutete, dass der Adressraum nur 15 Bit betrug und die Maschine nur auf insgesamt 32 KB Speicher zugreifen konnte. Der Adressraum wurde durch die Verwendung von weiteren zwei Bits der Adresse weiter begrenzt, um den Indexierungsmodus für alle logischen und arithmetischen (dh nicht verzweigungsfreien) Befehle anzuzeigen. Diese Bits steuerten Funktionen wie, ob die Adresse nach- oder vor-dekrementiert werden soll, was für die Konstruktion von Schleifen äußerst nützlich ist. Aber da all diese Bits bereits berücksichtigt waren, standen in diesen Anweisungen nur 13 für Adressen zur Verfügung, was bedeutet, dass nur 8 KB direkt adressiert werden konnten. Das bedeutete, dass der Hauptspeicher in vier 8-KB-Blöcke aufgeteilt wurde. Um auf Speicher außerhalb der 8 KB zuzugreifen, in denen sich der Befehl befand, mussten die Datenbytes, auf die verwiesen wurde, eine indirekte Adresse enthalten, die auf eine andere Stelle im Speicher zeigte.

Als der 2650 1972 entwickelt wurde, waren diese Einschränkungen des Adressraums aufgrund der geringen Größe und der hohen Kosten des statischen RAM- Speichers, der typischerweise bei diesen Prozessoren verwendet wird, nicht signifikant . Zu dieser Zeit enthielten Maschinen normalerweise 2 oder 4 KB RAM. Aber mit der zunehmenden Verwendung von dynamischem RAM ab Mitte der 1970er Jahre wurden Maschinen mit 8 und 16 KB RAM und schließlich 64 KB üblich und das Adressierungssystem des 2650 wurde zu einem erheblichen Hindernis.

Der 2650 enthielt auch einen On-Die- Call-Stack , anstatt die üblichere Lösung, die einen Speicherort für den Stack reserviert. Der Stapelzeiger wurde in PSW in drei Bits gehalten. Ein On-Die-Stack ist viel schneller, da direkt auf die Daten zugegriffen werden kann, ohne darauf zu warten, dass sie aus dem externen Speicher gelesen werden, aber er nimmt auch Platz auf dem Die ein und ist aufgrund praktischer Kompromisse immer in seiner Größe begrenzt. Beim 2650 war der Stack nur acht 15-Bit-Einträge tief, was im Allgemeinen viel zu klein ist, um für höhere Sprachen verwendet zu werden .

Obwohl es neun verschiedene Adressierungsmodi gab , verhinderten das Fehlen von 16-Bit-Registern und der 13-15-Bit-Adressraum eine weit verbreitete Verwendung. Trotzdem war ein Betriebssystem ("2650 DOS") verfügbar, zusammen mit 8-KB- und 12-KB- BASIC- Interpretern (verkauft von der Central Data Corporation USA) und vielen Spielen im Stil von Hunt the Wumpus . Die meisten Programme wurden in Assembler geschrieben .

Verwendet

Signetics verkaufte 2650-basierte Mikroprozessor-Entwicklungsboards , zuerst den PC1001 und dann seinen Nachfolger, den PC1500 "Adaptable Board Computer", der zwischen 165 und 400 AUD kostet. Der Chip allein wurde für rund 20 AUD verkauft. Mehrere Hardwarekonstruktionsprojekte und Programmierartikel wurden in Zeitschriften wie Electronics Australia und Elektor veröffentlicht und entsprechende Kits wurden von Elektronikgeschäften verkauft. Diese Faktoren führten dazu, dass es von einer Reihe von Hobbyisten in vielen Ländern wie Australien, USA, Großbritannien, den Niederlanden und Deutschland verwendet wurde.

Zwei Arten von Videospielkonsolen verwendet die Signetics 2650 oder 2650A. Die erste Konsolengruppe basiert auf dem Signetics 2636 Video-Display-Controller ; das 1292 Advanced Programmable Video System und der eng verwandte Interton Video Computer 4000 gehören zu dieser Gruppe. Diese wurden 1976 bzw. 1978 in Deutschland veröffentlicht. Die zweite Konsolengruppe basierte auf dem Signetics 2637 als Video-Display-Controller ; Emerson Arcadia 2001, das 1982 erschienen ist und als CPU eine Signetics 2650 mit 3,58 MHz verwendet, gehört zu dieser Gruppe zusammen mit vielen anderen Software-kompatiblen (Leonardo, Hanimex MPT-03 etc.).

Mindestens fünf münzbetriebene Videospiele wurden in den 1970er Jahren veröffentlicht, die die 2650-CPU verwendeten – Atari Quiz Show , Meadows Games 3D Bowling , Meadows Games Gypsy Juggler , Cinematronics Embargo und ein Klon von Space Invaders von Zaccaria namens The Invaders (1978) (Original von Taito verwendet eine Intel 8080 CPU).

Der italienische Spielehersteller Zaccaria hat 28 Flipperautomaten auf Basis der 2650-CPU veröffentlicht. Ihr Nachfolgeunternehmen MrGame veröffentlicht vier weitere Flipperautomaten mit dem 2650. Zaccaria scheint sein Design ebenfalls an Technoplay lizenziert zu haben, und mehrere weitere Flipperautomaten wurden mit Variationen von Zaccarias Leiterplattendesigns veröffentlicht.

Mindestens zwei münzbetriebene Videospiele wurden in den 1980er Jahren mit dem 2650 veröffentlicht. Hunchback und Hunchback Olympic .

Der Prozessor wurde auch im Signetics Instructor 50 verwendet , einem kleinen Computer, der entwickelt wurde, um die Verwendung und Programmierung der Signetics 2650 CPU zu lehren.

Der 2650 wurde auch in einigen großen Geräten wie dem Tektronix 8540 verwendet, einem Mikroprozessor-Softwareentwicklungssystem, das verschiedene In-Circuit-Emulator- , Trace-Speicher- und Logikanalysatorkarten für das Echtzeit-Debugging von Mikroprozessorsystemen unterstützte, wie es in den 1980er Jahren praktiziert wurde . Der 2650 stellte die grundlegenden Betriebssystemfunktionen, die Datenübertragung und die Schnittstelle zu einem Host-Computer oder einem seriellen Computerterminal bereit.

Als Mikrocontroller eignete sich der Prozessor aufgrund seiner umfangreichen I/O-Unterstützung am besten:

- Single-Bit-I/O-Pins am Prozessor (Sense/Flag-Bits)

- Signale zur direkten Adressierung von zwei 8-Bit-I/O-Ports (Steuer- und Datenports) unter Verwendung von Einzelbyte-Befehlen ( Port-I/O ). Dadurch wurde die aufwändige Hardware umgangen, die andere Systeme für speicherabgebildete I/Os benötigen

- Signale zur Adressierung weiterer 256 I/O-Ports unter Verwendung einer 8-Bit-Adresse und Zwei-Byte-Befehlen, wiederum um die erforderliche Hardware (Adressdecodierung) zu begrenzen. Philips betonte diesen Einsatz als Mikrocontroller mit einem Demonstrationsprogramm, in dem der 2650 ein intelligentes Aufzugssystem steuert. Außerdem zeigten sie auf Messen den 2650, der einen Miniatur-"Sort-and-Stack"-Roboter steuerte

Industrielles Mikrocomputersystem – IMS

Ab 1979 verkaufte Philips für kurze Zeit einen modularen 2650-Computer namens 'IMS' - Industrial Microcomputer System, basierend auf dem Eurocard- Format in einem 19"-Rack. Er enthielt CPU , PROM, RAM , Eingabe-, Ausgabe- und Fernschreibermodule System war als intelligentere speicherprogrammierbare Steuerung gedacht und fügte später die Module DEBUG, DISPLAY, INTERRUPT und MODEST ((E)PROM-Programmierer) hinzu.

Die Architektur

Der 2650 wurde in einem 40-poligen DIL- Gehäuse aus Kunststoff oder Keramik geliefert . Ein externes einphasiges Taktsignal und eine einzelne 5V-Versorgung wurden benötigt.

Der 2650 hatte im Vergleich zu anderen Mikroprozessoren der Zeit viele ungewöhnliche Eigenschaften:

- Es war ein vollständig statischer NMOS-8-Bit-Mikroprozessor. Die statische Natur war für die damalige Zeit ungewöhnlich und bedeutete, dass der Prozessor einfach durch Stoppen des Taktsignals angehalten werden konnte. Programmierer nutzten diese Funktion dankbar, um ein Programm mit einem Druckknopfschalter zur Erzeugung der Taktimpulse in einem "Einzelschritt" zu durchlaufen.

- Einzigartig war der im Prozessor integrierte 8-stufige 15 Bit breite Stack für die Unterprogramm- und Interrupt-Rücksprungadressen. Der Stapelzeiger verwendet 3 Bit des oberen Statusregisters. Dies bedeutete, dass Unterprogramme und Interrupts nur 8 Ebenen tief verschachtelt werden konnten.

- Der Prozessor hatte nur 13 echte Adressleitungen, weitere 2 Adressleitungen waren mit einem 2-Bit-'Page-Register' verbunden, was einen Adressraum von 32 KB ergibt. Das Seitenregister wurde gesetzt, als ein absoluter (direkter) Verzweigungsbefehl ausgeführt wurde, der eine volle 15-Bit-Adresse verwendet. Alle logischen und arithmetischen Befehle verwendeten eine 13-Bit-Adresse, die durch den Inhalt des Seitenregisters erweitert wurde, wodurch ihr Umfang auf eine 8-KB-Seite beschränkt wurde. Diese 2 oberen Adressleitungen wurden auch verwendet (gemultiplext), um den entsprechenden E/A-Port während der E/A-Operationen auszuwählen (Steuerungsport, Datenport oder erweiterter Port).

- Obwohl der 2650 nur einen Interrupt-Eingang hatte, war dies ein „vektorisierter“ Interrupt – das unterbrechende Gerät musste eine Null-relative Verschiebung auf den Datenbus setzen, die als Operand eines ZBSR verwendet wurde (Nullverzweigung zum Unterprogramm relativ). Anweisung, zu der angegebenen Interrupt-Routine zu verzweigen. Daher könnten bei indirekter Adressierung maximal 30 Interrupt-Vektoren in den ersten 64 Bytes des Speichers gespeichert werden. (Die ersten drei Bytes wurden benötigt, um eine unbedingte Verzweigung zur 'Reset'-Routine zu halten). Auch dieser vektorisierte Interrupt erinnert an den Minicomputer PDP-11 .

Befehlssatz

Obwohl der 2650 im Grunde ein 8-Bit-Mikroprozessor ist, sind 64 Opcodes tatsächlich 9-Bit und weitere 32 Opcodes sind 11-Bit (unter Verwendung von Bits im Adressfeld). Von den verbleibenden 128 8-Bit-Opcodes sind 124 (126 beim 2650B) implementiert, was insgesamt 444 (446) Befehle ergibt.

Viele weitere Befehle sind verfügbar, da das Verhalten der Standardbefehle durch Setzen oder Löschen von Statusbits geändert werden kann: WC (mit oder ohne Übertrag) und COM (logischer oder arithmetischer Vergleich). Dies verdoppelte die Anzahl der Rotations-, Addier-, Subtraktions- und Vergleichsanweisungen.

Der Befehlssatz ist stark orthogonal : Alle logischen und arithmetischen Befehle können alle neun Adressierungsmodi verwenden:

- registrieren

- sofort

- PC relativ und PC relativ indirekt

- absolut und absolut indirekt

- absolut indiziert, absolut indiziert mit Auto-Inkrement und absolut indiziert mit Auto-Dekrement, sowohl direkt als auch indirekt

Das höchstwertige Bit aller relativen und absoluten Adressen wird verwendet, um eine Indirektion anzuzeigen .

Die einzigen Ausnahmen sind dort, wo die Opcodes bedeutungsloser Operationen für andere Zwecke verwendet werden:

- der Opcode für UND-Register Null mit Register Null wird für den HALT-Befehl verwendet.

- der Opcode für STORE-Register Null in Register Null wird für den NOP- Befehl verwendet.

Obwohl der Befehl LOAD Register null mit Register null bedeutungslos erscheinen würde und offiziell nicht unterstützt wurde, setzte er den Bedingungscode und wurde oft verwendet, um den Status dieses Registers zu bestimmen.

Indizierung

Bei allen arithmetischen und logischen Anweisungen mit absoluter (direkter) Adressierung werden die Bits 14 und 13 des Adressfeldes verwendet, um den Indexierungsmodus wie folgt anzuzeigen:

- 00 keine Indizierung

- 01 Indizierung mit Autoinkrement

- 10 Indizierung mit Auto-Dekrement

- 11 nur Indizierung

Wenn die Indizierung angegeben ist, wird das im Befehl definierte Register zum Indexregister, und die Quelle/das Ziel ist implizit Register Null. Für die indirekte Indizierung wird die Post-Indexierung verwendet, dh die indirekte Adresse wird zuerst aus dem Speicher geholt und dann der Index hinzugefügt.

Verzweigung

Der wahrscheinlich am meisten Minicomputer ähnliche Aspekt des 2650 ist die enorme Anzahl (62) von Verzweigungs-(Sprung-)Befehlen; alle diese Anweisungen könnten auch indirekt verwendet werden:

- BIRR und BIRA: Register inkrementieren und verzweigen wenn ungleich Null (R0, R1, R2 oder R3) mit relativer oder absoluter Adressierung

- BDRR und BDRA: Register dekrementieren und verzweigen, wenn nicht Null (R0, R1, R2 oder R3) mit relativer oder absoluter Adressierung

- BRNR und BRNA: Verzweigung wenn Register ungleich Null (R0, R1, R2 oder R3) mit relativer oder absoluter Adressierung

- BCTR und BCTA: Verzweigung bei Bedingung Wahr (Null, Größer als, Kleiner oder unbedingt) mit relativer oder absoluter Adressierung

- BCFR und BCFA: Verzweigung bei Bedingung False (Null, größer oder kleiner) mit relativer oder absoluter Adressierung.

- ZBRR: Verzweigung relativ zur Adresse Null

- BXA: branchenindiziert

Wie der Intel 8080 hatte der 2650 Anweisungen, um bedingt zu einer Subroutine zu verzweigen und von dieser zurückzukehren:

- BSTR und BSTA: Verzweigen in Unterprogramm bei Bedingung Wahr (Null, Größer als, Kleiner oder unbedingt) mit relativer oder absoluter Adressierung

- BSFR und BSFA: Verzweigung in Unterprogramm bei Bedingung False (Null, größer oder kleiner als) mit relativer oder absoluter Adressierung

- BSNR und BSNA: Sprung ins Unterprogramm, wenn Register ungleich Null (R0, R1, R2 oder R3) mit relativer oder absoluter Adressierung

- RETC: Rückkehr vom Unterprogramm unter der Bedingung Wahr (Null, größer als, kleiner als oder unbedingt)

- RETE: Rückkehr von Interrupt bei Bedingung Wahr (Null, größer als, kleiner als oder unbedingt)

- ZBSR: Verzweigung in Unterprogramm relativ zur Adresse Null

- BSXA: Verzweigung in das indizierte Unterprogramm

Nur die Verzweigungsbefehle mit absoluter Adressierung verwendeten alle 15 Bits des Adressfeldes als Adresse. Die Verwendung eines solchen Verzweigungsbefehls war daher die einzige Möglichkeit, die beiden Bits im Seitenregister (die die Bits 14 und 13 des Adressbusses steuern) zu setzen und die aktuelle 8-KB-Seite zu ändern.

Versionen

- 2650 Originalversion mit 1,25 MHz maximaler Taktfrequenz

- 2650A verbesserte Version (geringfügige Fertigungsänderungen zur Verbesserung der Stabilität) 1,25 MHz maximale Taktfrequenz

- 2650A-1 wie 2650A mit 2 MHz maximaler Taktfrequenz

- 2650B

- 2650B-1 wie 2650B mit 2 MHz maximaler Taktfrequenz

Der 2650B hatte die folgenden Änderungen und Verbesserungen gegenüber dem 2650A:

- Zwei neue Signale – „Bus Enable“ an Pin 15 und „Cycle Last“ an Pin 25.

- Die oberen Bits 3 und 4 des Programmstatusworts sind einstellbare und testbare Benutzer-Flags (nicht verwendet beim 2650A).

- Zwei neue Befehle zum Sichern und Wiederherstellen des unteren Statusregisters, um die Interrupt-Verarbeitung zu vereinfachen.

- Einzelbyte-Register R0-Befehle werden schneller ausgeführt (ein Zyklus statt zwei).

Zweite Quellen

1975 wurde Signetics an Philips verkauft und die 2650 wurde später in die Philips Semiconductors- Produktlinie aufgenommen. Sie machten eine Version des 2650 namens MAB2650A. Valvo, eine Tochtergesellschaft von Philips, verkaufte den 2650 in Deutschland. Valvo verkaufte auch den VA200 Single Board (Eurocard) 2650 Computer mit 4 KB PROM/EPROM, 1 KB RAM und vier I/O-Ports.

Andere Hersteller von lizenzierten Kopien des Chips waren Harris und Intersil .

Peripheriechips

Der 2650 wurde mit einer vollständigen Ergänzung von Peripheriechips geliefert:

- 2621 Video-Encoder (PAL)

- 2622 Video-Encoder (NTSC)

- 2636 Programmierbare Videoschnittstelle

- 2637 Universal-Videoschnittstelle

- 2651 Programmierbare Kommunikationsschnittstelle

- 2652 Multiprotokoll-Kommunikationsschaltung (inkl. Synchronous Data Link Control (SDLC))

- 2653 Polynomgenerator / Checker

- 2655 Programmierbare Peripherieschnittstelle

- 2656 SMI (Systemspeicherschnittstelle)

- 2657 Direkter Speicherzugriff

- 2661 Enhanced Programmable Communication Interface (EPCI)

- 2670 Anzeigezeichen- und Grafikgenerator

- 2671 Programmierbare Tastatur und Kommunikationscontroller

- 2672 Programmierbarer Video-Timing-Controller

- 2673 Videoattribut-Controller

Viele dieser Peripheriechips wurden so konzipiert, dass sie auch mit anderen Mikroprozessoren verwendet werden können, zum Beispiel schlägt das Datenblatt des 2672 vor, ihn mit einem Intel 8048- Mikrocontroller zu verwenden .

Philips Technical Note 083 beschreibt, wie der 2651 PCI an verschiedene andere Mikroprozessoren wie 8080, 8085, Z80, 8048 und 6800 angeschlossen wird

Nachkommen der seriellen Kommunikationschips 2651/2661 werden immer noch als Philips SC26-Serie verkauft.

2656 Systemspeicherschnittstelle

Der 2656 wurde speziell entwickelt, um den 2650 zu erweitern und mit ihm zu verbinden und einen 2-Chip-Computer zu ermöglichen. Es enthielt alles, was dem 2650 fehlte, um einen kompletten Computer zu bauen:

- 2 KB 8-Bit maskenprogrammierter ROM-Programmspeicher

- 128 Byte 8-Bit-RAM-Speicher

- Taktgenerator mit Quarz- oder RC-Netzwerk

- Power-On-Reset

- Acht Allzweck-I/O-Pins

Die I/O-Pins können als 8-Bit-I/O-Port verwendet oder programmiert werden, um Freigabesignale für zusätzliche RAM-, ROM- oder I/O-Ports zu erzeugen. Dies wurde durch Maskenprogrammierung eines programmierbaren Logik-Arrays im 2656 erreicht.

Um das Design zu entwickeln und zu testen, bevor es in die Produktion geht, verkaufte Philips das PC4000, ein 2656-Emulatorboard, das PROMs und FPLAs verwendet, um das ROM und PLA im 2656 zu emulieren.

Anmerkungen

Verweise

Zitate

Literaturverzeichnis

- Rowe, Jamieson (September 1976). "Die Signetik 2650" (PDF) . Elektronik australien .

Externe Links

- 2650 Emulatoren

- Datenblatt

- CPU-Welt der Signetics 2650-Familie

- Ausbilder 50 Old-computers.com

- Adaptable Board Computer Entwicklungssystem komplett mit 1 KiB PipBug Monitor und 512 Byte RAM

- der 2650 auf www.cpu-museum.com (archiviert)

- Electronics Australia 2650-Board bei gesternstechnology.com

- Signetics 2650: An IBM on a Chip Retrospektive im CPUSHACK Museum (16. Oktober 2016)

- Zaccaria The Invaders im Museum of the Game

- Ein 2650 Cross-Assembler ist verfügbar unter https://shop-pdp.net/index.php