Motorola 68000 - Motorola 68000

| Designer | Motorola |

|---|---|

| Bits | 16/32-Bit |

| Eingeführt | 1979 |

| Entwurf | CISC |

| Verzweigung | Bedingungscode |

| Endianität | Groß |

| Register | |

| Allgemeine Information | |

|---|---|

| Gestartet | 1979 |

| Entworfen von | Motorola |

| Leistung | |

| Datenbreite | 16 Bit |

| Adressbreite | 24 Bit |

| Architektur und Klassifizierung | |

| Befehlssatz | Motorola 68000-Serie |

| Physikalische Spezifikationen | |

| Transistoren | |

| Pakete) | |

| Geschichte | |

| Nachfolger | Motorola 68010 |

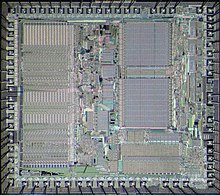

Der Motorola 68000 ( achtundsechzigtausend ; auch m68k genannt , Motorola 68k , achtundsechzigkay ) ist ein 16/32-Bit- Complex-Instruction-Set-Computer (CISC) -Mikroprozessor , der 1979 von Motorola Semiconductor Products Sector eingeführt wurde.

Das Design implementiert einen 32-Bit- Befehlssatz mit 32-Bit-Registern und einem internen 16-Bit- Datenbus . Der Adressbus ist 24 Bit lang und verwendet keine Speichersegmentierung , was die Programmierung erleichtert. Intern verwendet es eine 16-Bit - Datenarithmetik-Logik-Einheit (ALU) und zwei weitere 16-Bit-ALUs, die hauptsächlich für Adressen verwendet werden, und hat einen externen 16-Bit- Datenbus . Motorola bezeichnete ihn daher als 16/32-Bit-Prozessor.

Als einer der ersten weit verbreiteten Prozessoren mit einem 32-Bit-Befehlssatz, der für die damalige Zeit mit relativ hohen Geschwindigkeiten lief, war der 68k in den 1980er Jahren ein beliebtes Design. Es wurde in einer neuen Generation von PCs mit grafischer Benutzeroberfläche weit verbreitet verwendet , darunter Macintosh , Amiga , Atari ST und X68000 . Die Mega Drive- Konsole von 1988 wird ebenfalls von einem 68000 angetrieben.

Der 68k wurde bald um weitere Familienmitglieder erweitert und implementierte vollständige 32-Bit-ALUs als Teil der wachsenden Motorola 68000-Serie . Der ursprüngliche 68k ist im Allgemeinen software -aufwärtskompatibel mit dem Rest der Linie, obwohl er auf einen 16-Bit breiten externen Bus beschränkt ist.

Nach 42 Jahren in Produktion ist die 68000- Architektur immer noch im Einsatz.

Geschichte

Die erste weit verbreitete CPU von Motorola war die Motorola 6800 . Obwohl es ein leistungsfähiges Design war, wurde es von leistungsfähigeren Designs wie dem Zilog Z80 und weniger teuren Designs wie dem MOS Technology 6502 (MOS 6502) in den Schatten gestellt. Als sich die Verkaufsaussichten des 6800 verschlechterten, begann Motorola mit einem neuen Design, um es zu ersetzen. Daraus wurde das Motorola Advanced Computer System on Silicon-Projekt, kurz MACSS, das 1976 ins Leben gerufen wurde.

Das MACSS zielte darauf ab, eine völlig neue Architektur ohne Rückwärtskompatibilität mit dem 6800 zu entwickeln. Es behält schließlich einen Busprotokoll- Kompatibilitätsmodus für vorhandene 6800-Peripheriegeräte bei, und eine Version mit einem 8-Bit-Datenbus wurde produziert. Die Designer konzentrierten sich jedoch hauptsächlich auf die Zukunft oder die Vorwärtskompatibilität , was dem 68000-Design einen Vorsprung gegenüber späteren 32-Bit- Befehlssatzarchitekturen (ISAs) verschafft . Zum Beispiel sind die CPU-Register 32 Bit breit, obwohl nur wenige eigenständige Strukturen im Prozessor selbst mit 32 Bit gleichzeitig arbeiten. Das MACSS-Team stützte sich stark auf den Einfluss des Designs von Minicomputer- Prozessoren wie den PDP-11- und VAX- Systemen, die ähnlich auf Mikrocode basieren.

Mitte der 1970er Jahre eilten die Hersteller von 8-Bit-Mikroprozessoren um die Einführung der 16-Bit-Generation. National Semiconductor war 1973-1975 mit seinen IMP-16- und PACE- Prozessoren an erster Stelle , aber diese hatten Probleme mit der Geschwindigkeit. Intel hatte seit 1975 an seinem fortschrittlichen 16/32-Bit Intel iAPX 432 (alias 8800) und seit 1976 an seinem Intel 8086 gearbeitet (er wurde 1978 eingeführt, aber in Form des fast identischen 8088 in den IBM-PCs vor einigen Jahren weit verbreitet später). Die späte Ankunft in der 16-Bit-Arena bietet dem neuen Prozessor mehr Transistoren (ungefähr 40.000 aktive gegenüber 20.000 aktiven beim 8086), 32-Bit-Makrobefehle und eine allgemein anerkannte Benutzerfreundlichkeit.

Die ursprüngliche MC68000 wurde hergestellt unter Verwendung eines HMOS Verfahrens mit einer 3,5 & mgr; m Strukturbreite. Im September 1979 offiziell eingeführt, wurden die ersten Muster im Februar 1980 freigegeben, wobei die Produktionschips im November rezeptfrei erhältlich waren. Die anfänglichen Geschwindigkeitsstufen sind 4, 6 und 8 MHz . 1981 wurden 10-MHz-Chips und im Juni 1982 12,5-MHz-Chips verfügbar. Die 16,67-MHz-"12F"-Version des MC68000, die schnellste Version des ursprünglichen HMOS-Chips, wurde erst Ende der 1980er Jahre hergestellt.

IBM zog den 68000 für den IBM-PC in Betracht, entschied sich aber für den Intel 8088, weil der 68000 noch nicht fertig war; Walden C. Rhines schrieb, dass damit "Motorola mit seiner überlegenen Technologie den wichtigsten Designwettbewerb der letzten 50 Jahre verloren hat". (IBM Instruments verkaufte kurzzeitig die 68000-basierten IBM System 9000- Laborcomputersysteme.) Der 68k-Befehlssatz ist besonders gut geeignet, um Unix zu implementieren, und der 68000 und seine Nachfolger wurden die dominierenden CPUs für Unix-basierte Workstations, einschließlich Sun-Workstations und Apollo/ Domänen- Workstations. Der 68000 wird auch für Massenmarktcomputer wie Apple Lisa , Macintosh , Amiga und Atari ST verwendet . Der 68000 wird in Microsoft Xenix- Systemen sowie in einem frühen NetWare Unix-basierten Server verwendet. Der 68000 wird in der ersten Generation von Desktop- Laserdruckern verwendet , darunter der ursprüngliche LaserWriter von Apple Inc. und der HP LaserJet .

1981 stellte Motorola das Motorola 68000 Educational Computer Board vor , einen Einplatinencomputer für Bildungs- und Schulungszwecke, der zusätzlich zum 68000 selbst Speicher, E/A-Geräte, programmierbare Timer und Wire-Wrap-Bereich für kundenspezifische Schaltungen enthielt. Das Board wurde bis Anfang der 1990er Jahre an US-Colleges als Werkzeug zum Erlernen der Assemblerprogrammierung verwendet.

Im Jahr 1982 erhielt die 68000 ein kleineres Update für seine Befehlssatzarchitektur (ISA) zur Unterstützung des virtuellen Speichers und zu den entsprechen Popek und Goldberg Virtualisierungsanforderungen . Der aktualisierte Chip heißt 68010 . Es fügt auch einen neuen "Loop-Modus" hinzu, der kleine Schleifen beschleunigt und die Gesamtleistung bei gleichen Taktraten um etwa 10 % erhöht. Eine weitere erweiterte Version, die 31 Bit des Adressbusses freilegt, wurde als 68012 ebenfalls in kleinen Stückzahlen produziert .

Um kostengünstigere Systeme und Steuerungsanwendungen mit kleineren Speichergrößen zu unterstützen, führte Motorola ebenfalls 1982 den 8-Bit-kompatiblen MC68008 ein. Dies ist ein 68000 mit einem 8-Bit-Datenbus und einem kleineren (20-Bit) Adressbus. Nach 1982 widmete Motorola den Projekten 68020 und 88000 mehr Aufmerksamkeit .

Second-Sourcing

Mehrere andere Unternehmen waren Second-Source- Hersteller des HMOS 68000. Dazu gehörten Hitachi (HD68000), die die Feature-Größe für ihre 12,5-MHz-Version auf 2,7 µm verkleinerten , Mostek (MK68000), Rockwell (R68000), Signetics (SCN68000), Thomson / SGS-Thomson (ursprünglich EF68000 und später TS68000) und Toshiba (TMP68000). Toshiba war auch ein Second-Source-Hersteller des CMOS 68HC000 (TMP68HC000).

Verschlüsselte Varianten des 68000, die Hitachi FD1089 und FD1094, speichern Entschlüsselungsschlüssel für Opcodes und Opcode-Daten im batteriegepufferten Speicher und wurden in bestimmten Sega-Arcade-Systemen einschließlich System 16 verwendet , um Piraterie und illegale Raubkopien zu verhindern.

CMOS-Versionen

Der 68HC000, die erste CMOS- Version des 68000, wurde von Hitachi entwickelt und 1985 gemeinsam vorgestellt. Motorolas Version heißt MC68HC000, während Hitachis HD68HC000 heißt. Der 68HC000 bietet Geschwindigkeiten von 8–20 MHz. Abgesehen von der Verwendung von CMOS-Schaltungen verhielt es sich identisch mit dem HMOS MC68000, aber der Wechsel zu CMOS reduzierte seinen Stromverbrauch erheblich. Der ursprüngliche HMOS MC68000 verbrauchte bei einer Umgebungstemperatur von 25 °C unabhängig von der Taktrate etwa 1,35 Watt , während der MC68HC000 nur 0,13 Watt bei 8 MHz und 0,38 Watt bei 20 MHz verbrauchte. (Im Gegensatz zu CMOS-Schaltungen verbraucht HMOS im Leerlauf immer noch Strom, sodass der Stromverbrauch nur geringfügig von der Taktrate abhängt.) Apple hat den 68HC000 für den Macintosh Portable ausgewählt .

Motorola ersetzte 1990 den MC68008 durch den MC68HC001. Dieser Chip ähnelt in vielerlei Hinsicht dem 68HC000, aber sein Datenbus kann entweder im 16-Bit- oder 8-Bit-Modus betrieben werden, abhängig vom Wert eines Eingangspins beim Zurücksetzen. Somit kann er wie der 68008 in Systemen mit billigeren 8-Bit-Speichern eingesetzt werden.

Die spätere Entwicklung des 68000 konzentrierte sich auf modernere eingebettete Steuerungsanwendungen und On-Chip-Peripheriegeräte. Der 68EC000- Chip und der SCM68000-Kern entfernen den M6800-Peripheriebus und schließen den MOVE von SR-Befehlen aus Benutzermodusprogrammen aus, was 68EC000 und 68SEC000 zu den einzigen 68000-CPUs macht, die nicht zu 100% mit früheren 68000-CPUs kompatibel sind, wenn sie im Benutzermodus ausgeführt werden. Bei Ausführung im Supervisor-Modus gibt es keinen Unterschied. 1996 aktualisierte Motorola den Standalone-Core mit einer vollständig statischen Schaltung, die im Low-Power-Modus nur 2 µW verbrauchte, und nannte ihn MC68SEC000.

Motorola stellte die Produktion der HMOS MC68000 und MC68008 1996 ein, aber sein Spin-off-Unternehmen Freescale Semiconductor produzierte weiterhin die MC68HC000, MC68HC001, MC68EC000 und MC68SEC000 sowie die Mikrocontroller MC68302 und MC68306 und spätere Versionen der DragonBall- Familie. Die architektonischen Nachfahren des 68000, die Familien 680x0 , CPU32 und Coldfire , waren ebenfalls noch in Produktion. In jüngerer Zeit wurden mit der Schließung der Sendai-Fabrik alle 68HC000-, 68020-, 68030- und 68882-Teile eingestellt, sodass nur noch der 68SEC000 in Produktion ist.

Als Mikrocontroller-Kern

Da der 68000 von "echten" 32-Bit-Mikroprozessoren abgelöst wurde, wird er als Herzstück vieler Mikrocontroller verwendet . 1989 stellte Motorola den Kommunikationsprozessor MC68302 vor .

Anwendungen

Bei seiner Einführung wurde der 68000 erstmals in hochpreisigen Systemen eingesetzt, darunter Mehrbenutzer- Mikrocomputer wie der WICAT 150, frühe Alpha Microsystems- Computer, Sage II / IV , Tandy 6000 / TRS-80 Modell 16 und Fortune 32:16 ; Single-User - Workstations wie Hewlett-Packard 's HP 9000 Series 200 Systeme, die ersten Apollo / Domain Systeme, Sun Microsystems ' Sun-1 und das Corvus Konzept ; und Grafik - Terminals wie Digital Equipment Corporation 's VAXstation 100 und Silicon Graphics IRIS 1000 und 1200. Unix - Systeme schnell bewegten auf die besser in der Lage späteren Generationen der 68k - Linie, die in diesem Markt in den 1980er Jahren populär geblieben.

Mitte der 1980er Jahre machten sinkende Produktionskosten den 68000 für den Einsatz in Personal- und Heimcomputern geeignet , beginnend mit der Apple Lisa und dem Macintosh , gefolgt vom Commodore Amiga , Atari ST und Sharp X68000 . Andererseits war der Mikrocomputer Sinclair QL neben seinen Derivaten, wie dem Business-Terminal ICL One Per Desk, die kommerziell wichtigste Anwendung des 68008 . Helix Systems (in Missouri, USA) entwarf eine Erweiterung des SWTPC SS-50-Busses , den SS-64, und produzierte Systeme, die um den 68008-Prozessor herum gebaut wurden.

Während die Einführung von RISC und x86 die 68000-Serie als Desktop-/Workstation-CPU verdrängte, fand der Prozessor in Embedded- Anwendungen erheblichen Einsatz . Bis Anfang der 1990er Jahre konnten Stückzahlen von 68000 CPUs für weniger als 30 USD pro Teil erworben werden.

Videospiel - Hersteller verwendet , um die 68000 als das Rückgrat vieler Arcade - Spiele und Heimspielkonsolen : Ataris Food Fight von 1982, war einer der ersten 68000-basierten Arcade - Spiele. Andere enthalten Sega 's - System 16 , Capcom ' s CP - System und CPS-2 und SNK ‚s Neo Geo . In den späten 1980er Jahren war der 68000 preiswert genug, um Heimspielkonsolen wie Segas Mega Drive/Genesis- Konsole und auch den Mega CD- Aufsatz dafür zu betreiben (ein Mega CD-System hat drei CPUs, zwei davon 68000s). Die Multiprozessor- Konsole Atari Jaguar von 1993 verwendete einen 68000 als Unterstützungschip, obwohl einige Entwickler ihn aus Vertrautheit als Hauptprozessor verwendeten. Die Multiprozessor- Konsole von Sega Saturn von 1994 verwendete den 68000 als Sound-Coprozessor (so wie der Mega Drive/Genesis den Z80 als Co-Prozessor für Sound und/oder andere Zwecke verwendet). Bis 1995 hatte es der 68000 als Haupt-CPU in eine Handheld-Spielekonsole , Segas Genesis Nomad , geschafft.

Bestimmte Arcade-Spiele (wie Steel Gunner und andere basierend auf Namco System 2 ) verwenden eine duale 68000 CPU-Konfiguration, und es gibt auch Systeme mit einer dreifachen 68000 CPU-Konfiguration (wie Galaxy Force und andere basierend auf dem Sega Y Board), zusammen mit eine Quad-68000-CPU-Konfiguration, die von Jaleco (eine 68000er für Sound hat eine niedrigere Taktrate im Vergleich zu den anderen 68000er-CPUs) für Spiele wie Big Run und Cisco Heat verwendet wurde ; ein weiterer, fünfter 68000er (mit einer anderen Taktrate als die anderen 68000er CPUs) wurde im Jaleco Arcade-Spiel Wild Pilot für die Eingabe/Ausgabe (I/O)-Verarbeitung verwendet.

Auch als Embedded Controller war der 68000 sehr erfolgreich. Bereits 1981 wurden Laserdrucker wie der Imagen Imprint-10 über externe Boards gesteuert , die mit dem 68000 ausgestattet waren. Der erste HP LaserJet , der 1984 vorgestellt wurde, kam mit einem eingebauten 8 MHz 68000. Andere Druckerhersteller übernahmen den 68000, darunter Apple mit der Einführung des LaserWriter im Jahr 1985, dem ersten PostScript- Laserdrucker. Der 68000 wurde während des Rests der 1980er Jahre weiterhin in Druckern verwendet und blieb bis weit in die 1990er Jahre bei Low-End-Druckern bestehen.

Auch im Bereich industrieller Steuerungssysteme war der 68000 erfolgreich. Zu den Systemen, die von einem 68000 oder einem Derivat als Mikroprozessor profitierten, gehörten Familien von speicherprogrammierbaren Steuerungen (SPS), die von Allen-Bradley , Texas Instruments und später, nach der Übernahme dieser Division von TI, von Siemens hergestellt wurden . Benutzer solcher Systeme akzeptieren die Produktveralterung nicht im gleichen Maße wie private Benutzer, und es ist sehr wahrscheinlich, dass viele 68000-basierte Controller, obwohl sie vor über 20 Jahren installiert wurden, bis weit in das 21. Jahrhundert hinein zuverlässig funktionieren werden.

In einer Reihe von digitalen Oszilloskopen aus den 80er Jahren wurde das 68000 als Prozessor für die Wellenformanzeige verwendet; Einige Modelle, einschließlich des LeCroy 9400/9400A, verwenden den 68000 auch als mathematischen Signalprozessor (einschließlich Addition, Subtraktion, Multiplikation und Division von zwei Signalen/Referenzen/Signalformspeichern) und einige digitale Oszilloskope mit dem 68000 (einschließlich 9400/9400A .) ) kann auch schnelle Fourier-Transformationsfunktionen an einer Wellenform ausführen .

Die auf der 68000-Architektur basierenden 683XX- Mikrocontroller werden in Netzwerk- und Telekommunikationsgeräten, TV-Set-Top-Boxen, Labor- und medizinischen Instrumenten und sogar Taschenrechnern verwendet. Der MC68302 und seine Derivate wurden in vielen Telekommunikationsprodukten von Cisco, 3com, Ascend, Marconi, Cyclades und anderen verwendet. Frühere Modelle der Palm- PDAs und des Handspring-Visiers verwendeten den DragonBall , ein Derivat des 68000. AlphaSmart verwendete die DragonBall-Familie in späteren Versionen seiner tragbaren Textverarbeitungsprogramme. Texas Instruments verwendet den 68000 in seinen High-End-Grafikrechnern, den Serien TI-89 und TI-92 sowie Voyage 200 .

Eine modifizierte Version des 68000 bildete die Grundlage des IBM XT/370 Hardware-Emulators des System 370 Prozessors.

Die Architektur

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Adressbus

Der 68000 hat einen externen 24-Bit-Adressbus und zwei Byte-Select-Signale "ersetzt" A0. Diese 24 Leitungen können somit 16 MB physikalischen Speicher mit Byte-Auflösung adressieren. Die Adressspeicherung und -berechnung verwendet intern 32 Bits; die 8 höherwertigen Adressbits werden jedoch aufgrund des physischen Fehlens von Gerätepins ignoriert. Dies ermöglicht es, Software auszuführen, die für einen logisch flachen 32-Bit- Adressraum geschrieben wurde , während nur auf einen physischen 24-Bit-Adressraum zugegriffen wird. Motorolas Absicht mit dem internen 32-Bit-Adressraum war die Aufwärtskompatibilität, die es möglich machte, 68000-Software zu schreiben, die die Vorteile der späteren 32-Bit-Implementierungen des 68000-Befehlssatzes voll ausnutzen würde.

Dies hinderte Programmierer jedoch nicht daran, zukunftsinkompatible Software zu schreiben. "24-Bit"-Software, die das obere Adressbyte verworfen oder für andere Zwecke als die Adressierung verwendet hat, kann bei 32-Bit-68000-Implementierungen fehlschlagen. Beispielsweise verwendeten frühe (vor 7.0) Versionen von Apples Mac OS das High-Byte von Speicherblock-Master-Zeigern, um Flags wie Locked und Purgeable zu halten . Spätere Versionen des Betriebssystems verlegten die Flaggen an einen nahe gelegenen Ort, und Apple begann mit der Veröffentlichung des 1989er Mac IIci mit der Auslieferung von Computern, die über „ 32-Bit-saubere “ ROMs verfügten.

Die 68000-Familie speichert Multi-Byte-Ganzzahlen in Big-Endian- Reihenfolge im Speicher .

Interne Register

Die CPU hat acht 32-Bit-Allzweck- Datenregister (D0-D7) und acht Adressregister (A0-A7). Das letzte Adressregister ist der Stapelzeiger , und Assembler akzeptieren das Etikett SP als Äquivalent zu A7. Dies war damals in vielerlei Hinsicht eine gute Anzahl von Registern. Es war klein genug, um dem 68000 zu ermöglichen, schnell auf Interrupts zu reagieren (selbst im schlimmsten Fall, wenn alle 8 Datenregister D0–D7 und 7 Adressregister A0–A6 gespeichert werden mussten, insgesamt 15 Register), und dennoch groß genug, um machen die meisten Berechnungen schnell, da sie vollständig im Prozessor ausgeführt werden könnten, ohne Teilergebnisse im Speicher zu behalten. (Beachten Sie, dass eine Ausnahmeroutine im Supervisor-Modus auch den User-Stack-Pointer A7 speichern kann, was insgesamt 8 Adressregister ergeben würde. Das Design des Dual-Stack-Pointers (A7 und Supervisor-Modus A7') des 68000 macht dies jedoch normalerweise unnötig, außer wenn ein Taskwechsel in einem Multitasking-System durchgeführt wird.)

Das Vorhandensein der beiden Registertypen ermöglicht die gleichzeitige Ausführung einer 32-Bit-Adresse und einer 16-Bit-Datenberechnung. Dies führt zu einer reduzierten Befehlsausführungszeit, da Adressen und Daten parallel verarbeitet werden können.

Statusregister

Der 68000 verfügt über ein 16-Bit-Statusregister. Die oberen 8 Bits sind das Systembyte, und dessen Modifikation ist privilegiert. Die unteren 8 Bits sind das Benutzerbyte, das auch als Bedingungscoderegister (CCR) bekannt ist und dessen Änderung nicht privilegiert ist. Die 68000-Vergleichs-, Arithmetik- und Logikoperationen modifizieren Bedingungscodes, um ihre Ergebnisse für spätere bedingte Sprünge aufzuzeichnen. Die Bedingungscodebits sind "Null" (Z), "Übertrag" (C), "Überlauf" (V), "Verlängern" (X) und "Negativ" (N). Das Flag "extend" (X) verdient besondere Erwähnung, da es vom Carry-Flag getrennt ist . Dies ermöglicht, dass das zusätzliche Bit aus arithmetischen, logischen und Schiebeoperationen für den Steuerungsfluss und die Verknüpfung vom Übertrag getrennt wird.

Befehlssatz

Die Designer versuchten, die Assemblersprache orthogonal zu gestalten . Das heißt, Befehle sind in Operationen und Adressmodi unterteilt , und fast alle Adressmodi sind für fast alle Befehle verfügbar. Es gibt 56 Befehle und eine minimale Befehlsgröße von 16 Bit. Viele Befehle und Adressierungsmodi sind länger, um mehr Adress- oder Modusbits zu enthalten.

Berechtigungsstufen

Die CPU und später die ganze Familie implementiert zwei Privilegienebenen. Der Benutzermodus bietet Zugriff auf alles außer privilegierten Anweisungen wie Kontrollen auf Interrupt-Ebene. Das Supervisor-Privileg gibt Zugriff auf alles. Ein Interrupt wird immer zum Supervisor. Das Supervisor-Bit wird im Statusregister gespeichert und ist für Anwenderprogramme sichtbar.

Ein Vorteil dieses Systems besteht darin, dass die Supervisor-Ebene einen separaten Stack-Pointer hat. Dies ermöglicht es einem Multitasking- System, sehr kleine Stapel für Aufgaben zu verwenden, da die Designer nicht den Speicher zuweisen müssen, der erforderlich ist, um die Stapelrahmen eines maximalen Stapels von Interrupts zu halten.

Unterbrechungen

Die CPU kennt sieben Interrupt- Level. Die Stufen 1 bis 5 sind streng priorisiert. Das heißt, ein Interrupt mit einer höheren Nummer kann immer einen Interrupt mit einer niedrigeren Nummer unterbrechen. Im Statusregister ermöglicht ein privilegierter Befehl das Einstellen des aktuellen minimalen Interrupt-Levels, wodurch Interrupts mit niedrigerer oder gleicher Priorität blockiert werden. Wenn beispielsweise der Interrupt-Level im Statusregister auf 3 gesetzt ist, können höhere Level von 4 bis 7 eine Ausnahme verursachen. Level 7 ist ein pegelgetriggerter nicht maskierbarer Interrupt (NMI). Level 1 kann von jedem höheren Level unterbrochen werden. Level 0 bedeutet kein Interrupt. Die Ebene wird im Statusregister gespeichert und ist für Programme auf Benutzerebene sichtbar.

Prozessalarme werden über drei Eingänge an die CPU gemeldet, die die höchste anstehende Alarmpriorität kodieren. Zum Codieren der Interrupts ist normalerweise ein separater Codierer erforderlich, obwohl es bei Systemen, die nicht mehr als drei Hardware-Interrupts benötigen, möglich ist, die Interrupt-Signale auf Kosten einer höheren Software-Komplexität direkt mit den codierten Eingängen zu verbinden. Der Interrupt-Controller kann so einfach wie ein 74LS148- Prioritätsencoder sein oder kann Teil eines Peripheriechips mit sehr großer Integration (VLSI) sein, wie dem Multifunktions-Peripheriegerät MC68901 (verwendet in der Atari ST- Reihe von Computern und Sharp X68000 ), die auch einen UART , einen Timer und eine parallele E/A bereitstellte.

Die "Ausnahmetabelle" ( Interrupt-Vektortabellen- Interrupt-Vektoradressen) ist auf die Adressen 0 bis 1023 festgelegt und erlaubt 256 32-Bit-Vektoren. Der erste Vektor (RESET) besteht aus zwei Vektoren, nämlich der Startstapeladresse und der Startcodeadresse. Vektoren , 3 bis 15 werden verwendet , um verschiedene Fehler zu melden: Busfehler , Adressfehler, illegale Instruktion , Null Division , CHK und CHK2 Vektor, Privilegverletzung (zu Block Privilegienerweiterung ) und einige reservierten Vektoren , die Linie 1010 Emulator wurde, Linie 1111 Emulator und Hardware- Haltepunkt . Vektor 24 startet die echten Interrupts: Störende Interrupts (keine Hardwarebestätigung) und Level 1 bis Level 7 Autovektoren, dann die 16 TRAP-Vektoren, dann einige weitere reservierte Vektoren, dann die benutzerdefinierten Vektoren.

Da zumindest der Startcode-Adressvektor beim Zurücksetzen immer gültig sein muss, umfassten die Systeme üblicherweise einen nichtflüchtigen Speicher (zB ROM ), der bei der Adresse Null beginnt, um die Vektoren und den Bootstrap- Code zu enthalten . Für ein Allzwecksystem ist es jedoch wünschenswert, dass das Betriebssystem die Vektoren zur Laufzeit ändern kann. Dies wurde oft erreicht, indem entweder die Vektoren im ROM auf eine Sprungtabelle im RAM gezeigt wurden , oder durch die Verwendung einer Bankumschaltung , um zu ermöglichen, dass das ROM zur Laufzeit durch RAM ersetzt wurde.

Der 68000 erfüllt nicht die Virtualisierungsanforderungen von Popek und Goldberg für eine vollständige Prozessorvirtualisierung, da er über einen einzigen unprivilegierten Befehl verfügt, "MOVE from SR", der Software-Lesezugriff im Benutzermodus auf eine kleine Menge privilegierter Zustände ermöglicht. Die 68EC000 und 68SEC000, spätere Derivate des 68000, erfüllen jedoch die Anforderungen, da der Befehl "MOVE from SR" privilegiert ist. Dieselbe Änderung wurde auf den CPUs 68010 und später eingeführt.

Der 68000 kann auch virtuellen Speicher nicht ohne weiteres unterstützen , was die Fähigkeit zum Abfangen und Wiederherstellen nach einem fehlgeschlagenen Speicherzugriff erfordert. Der 68000 bietet zwar eine Busfehlerausnahme, die zum Abfangen verwendet werden kann, aber er speichert nicht genügend Prozessorstatus, um den fehlerhaften Befehl wieder aufzunehmen, sobald das Betriebssystem die Ausnahme behandelt hat. Mehreren Unternehmen gelang es, 68000-basierte Unix-Workstations mit virtuellem Speicher herzustellen, die unter Verwendung von zwei 68000-Chips arbeiteten, die parallel mit unterschiedlichen Takten laufen. Wenn der "führende" 68000 einen schlechten Speicherzugriff entdeckte, würde zusätzliche Hardware den "Haupt" 68000 unterbrechen, um zu verhindern, dass er auch auf den schlechten Speicherzugriff stößt. Diese Unterbrechungsroutine würde die virtuellen Speicherfunktionen handhaben und den "führenden" 68000 im richtigen Zustand neu starten, um den ordnungsgemäß synchronisierten Betrieb fortzusetzen, wenn der "Haupt" 68000 von der Unterbrechung zurückkehrte.

Diese Probleme wurden in der nächsten großen Überarbeitung der 68k-Architektur mit der Veröffentlichung des MC68010 behoben. Die Busfehler- und Adressfehler-Ausnahmen drücken eine große Menge an internem Zustand auf den Supervisor-Stack, um die Wiederherstellung zu erleichtern, und der Befehl "MOVE from SR" wurde privilegiert. Ein neuer unprivilegierter "MOVE from CCR"-Befehl wird zur Verwendung durch die Benutzermodus-Software an seiner Stelle bereitgestellt; ein Betriebssystem kann auf Wunsch "MOVE from SR"-Anweisungen im Benutzermodus abfangen und emulieren.

Details zum Befehlssatz

Die Standard- Adressierungsmodi sind:

- Direkt anmelden

- Datenregister, zB "D0"

- Adressregister, zB "A0"

- Indirekt registrieren

- Einfache Adresse, zB (A0)

- Adresse mit Postinkrement, zB (A0)+

- Adresse mit Vordekrement, zB −(A0)

- Adresse mit 16-Bit-Offset mit Vorzeichen, zB 16(A0)

- Register indirekt mit Indexregister & 8-Bit-Offset mit Vorzeichen zB 8(A0,D0) oder 8(A0,A1)

- Beachten Sie, dass für (A0)+ und –(A0) der tatsächliche Inkrement- oder Dekrementwert von der Operandengröße abhängt: Ein Byte-Zugriff passt das Adressregister um 1, ein Wort um 2 und ein Long um 4.

- PC (Programmzähler) relativ mit Verschiebung

- Relativer 16-Bit-Offset mit Vorzeichen, zB 16(PC). Dieser Modus war sehr nützlich für positionsunabhängigen Code.

- Relativ mit 8-Bit-Offset mit Vorzeichen mit Index, zB 8(PC,D2)

- Absoluter Speicherort

- Entweder eine Zahl, zB "$4000", oder ein vom Assembler übersetzter symbolischer Name

- Die meisten 68000-Assembler verwendeten das "$"-Symbol für hexadezimal anstelle von "0x" oder einem nachgestellten H.

- Es gab 16- und 32-Bit-Versionen dieses Adressierungsmodus

- Sofortmodus

- In der Anweisung gespeicherte Daten, zB "#400"

- Schneller Sofortmodus

- 3-Bit ohne Vorzeichen (oder 8-Bit mit Vorzeichen mit moveq) mit Wert im Opcode gespeichert

- In addq und subq entspricht 0 8

- zB moveq #0,d0 war schneller als clr.l d0 (obwohl beide D0 gleich 0 machten)

Plus: Zugriff auf das Statusregister und in späteren Modellen auf weitere Sonderregister.

Die meisten Befehle haben Punkt-Buchstaben-Suffixe, wodurch Operationen an 8-Bit-Bytes (".b"), 16-Bit-Wörtern (".w") und 32-Bit-Längen (".l") erfolgen können.

Wie bei vielen CPUs ihrer Ära variierte die Zykluszeit einiger Befehle je nach Quelloperand(en). Zum Beispiel benötigt der vorzeichenlose Multiplikationsbefehl (38+2n) Taktzyklen, um abgeschlossen zu sein, wobei 'n' gleich der Anzahl der im Operanden gesetzten Bits ist. Um eine Funktion zu erstellen, die eine feste Zykluszahl benötigte, musste nach dem Multiplikationsbefehl ein zusätzlicher Code hinzugefügt werden. Dies würde typischerweise zusätzliche Zyklen für jedes Bit verbrauchen, das im ursprünglichen Multiplikationsoperanden nicht gesetzt wurde.

Die meisten Befehle sind dyadisch , dh die Operation hat eine Quelle und ein Ziel, und das Ziel wird geändert. Bemerkenswerte Anweisungen waren:

- Arithmetik: ADD, SUB, MULU (Vorzeichenlose Multiplikation), MULS (Vorzeichenbehaftete Multiplikation), DIVU, DIVS, NEG (Additive Negation) und CMP (eine Art Vergleich durch Subtrahieren der Argumente und Setzen der Statusbits, aber nicht speichern das Ergebnis)

- Binärcodierte Dezimalarithmetik: ABCD, NBCD und SBCD

- Logik: EOR (exklusives oder), AND, NOT (logisches nicht), OR (inklusive oder)

- Shifting: (logische, dh Rechtsverschiebungen setzen Null in das höchstwertige Bit) LSL, LSR, ( arithmetische Verschiebungen , dh Vorzeichenerweiterung des höchstwertigen Bits) ASR, ASL, (rotiert durch eXtend und nicht) ROXL, ROXR, ROL, ROR

- Bittest und Manipulation im Speicher oder Datenregister: BSET (auf 1 gesetzt), BCLR (auf 0 löschen), BCHG (invertieren) und BTST (keine Änderung). Alle diese Befehle testen zuerst das Zielbit und setzen (löschen) das CCR-Z-Bit, wenn das Zielbit jeweils 0 (1) ist.

- Multiprocessing- Steuerung: TAS, test-and-set , führte eine unteilbare Busoperation durch, die die Verwendung von Semaphoren ermöglichte , um mehrere Prozessoren zu synchronisieren, die sich einen einzigen Speicher teilen

- Kontrollfluss: JMP (Sprung), JSR (Sprung zum Unterprogramm), BSR (Relativer Adresssprung zum Unterprogramm), RTS (Rückkehr vom Unterprogramm ), RTE (Rückkehr von Ausnahme , dh einem Interrupt), TRAP (Auslösen einer Software-Ausnahme ähnlich) auf Software-Interrupt), CHK (eine bedingte Software-Ausnahme)

- Verzweigung: Bcc (wobei "cc" einen von 14 Tests der Bedingungscodes im Statusregister spezifiziert: gleich, größer als, kleiner als, Übertrag und die meisten Kombinationen und logischen Inversionen, die aus dem Statusregister verfügbar sind). Die verbleibenden zwei möglichen Bedingungen (immer wahr und immer falsch) haben separate Befehlsmnemoniken, BRA (immer verzweigen) und BSR (zu Unterprogramm verzweigen).

- Dekrementieren und verzweigen: DBcc (wobei "cc" wie bei den Verzweigungsbefehlen war), die, sofern die Bedingung falsch war , das niedrige Wort eines D-Registers dekrementiert und, wenn das Ergebnis nicht -1 war ($FFFF) , verzweigt zu einem Ziel. Diese Verwendung von −1 anstelle von 0 als Abschlusswert ermöglichte die einfache Codierung von Schleifen, die nichts tun mussten, wenn der Zählerstand 0 war, ohne dass eine weitere Überprüfung vor dem Eintritt in die Schleife erforderlich war. Dies erleichterte auch die Verschachtelung von DBcc.

68EC000

Der 68EC000 ist eine kostengünstige Version des 68000 mit einer etwas anderen Pinbelegung, die für Embedded-Controller-Anwendungen entwickelt wurde. Der 68EC000 kann entweder einen 8-Bit- oder 16-Bit -Datenbus haben , umschaltbar beim Reset.

Die Prozessoren sind in verschiedenen Geschwindigkeiten erhältlich, darunter 8- und 16- MHz- Konfigurationen, die jeweils 2.100 und 4.376 Dhrystones produzieren. Diese Prozessoren haben keine Gleitkommaeinheit , und es ist schwierig, einen FPU- Coprozessor ( MC68881/2 ) mit einem zu implementieren, da der EC-Serie die notwendigen Coprozessor-Befehle fehlen.

Der 68EC000 wurde als Controller in vielen Audioanwendungen verwendet, einschließlich Ensoniq- Musikinstrumenten und -Soundkarten , wo er Teil des MIDI- Synthesizers war. Auf Ensoniq-Soundboards bot der Controller mehrere Vorteile im Vergleich zu Mitbewerbern ohne CPU an Bord. Der Prozessor ermöglichte es, das Board so zu konfigurieren, dass es verschiedene Audioaufgaben wie die MPU-401- MIDI-Synthese oder die MT-32- Emulation ohne Verwendung eines TSR- Programms ausführen konnte . Dadurch wurde die Softwarekompatibilität verbessert, die CPU-Auslastung gesenkt und die Speicherauslastung des Hostsystems eliminiert.

Der Motorola 68EC000-Kern wurde später in den m68k-basierten DragonBall- Prozessoren von Motorola/ Freescale verwendet .

Es wurde auch als Sound-Controller in der Sega Saturn -Spielkonsole und als Controller für die HP JetDirect Ethernet- Controller-Boards für die HP LaserJet- Drucker Mitte der 1990er Jahre verwendet.

Beispielcode

Der folgende 68000- Assembly- Code ist für eine Subroutine namens strtolower, die eine nullterminierte Zeichenfolge von 8-Bit-Zeichen in eine Zielzeichenfolge kopiert und alle alphabetischen Zeichen in Kleinbuchstaben umwandelt.

00100000

00100000 4E56 0000

00100004 306E 0008

00100008 326E 000C

0010000C 1018

0010000E 0C40 0041

00100012 6500 000E

00100016 0C40 005A

0010001A 6200 0006

0010001E 0640 0020

00100022 12C0

00100024 66E6

00100026 4E5E

00100028 4E75

0010002A

|

; strtolower:

; Copy a null-terminated ASCII string, converting

; all alphabetic characters to lower case.

;

; Entry parameters:

; (SP+0): Source string address

; (SP+4): Target string address

org $00100000 ;Start at 00100000

strtolower public

link a6,#0 ;Set up stack frame

movea 8(a6),a0 ;A0 = src, from stack

movea 12(a6),a1 ;A1 = dst, from stack

loop move.b (a0)+,d0 ;Load D0 from (src), incr src

cmpi #'A',d0 ;If D0 < 'A',

blo copy ;skip

cmpi #'Z',d0 ;If D0 > 'Z',

bhi copy ;skip

addi #'a'-'A',d0 ;D0 = lowercase(D0)

copy move.b d0,(a1)+ ;Store D0 to (dst), incr dst

bne loop ;Repeat while D0 <> NUL

unlk a6 ;Restore stack frame

rts ;Return

end

|

Das Unterprogramm erstellt einen Aufrufrahmen unter Verwendung des Registers A6 als Rahmenzeiger. Diese Art von Aufrufkonvention unterstützt wiedereintretenden und rekursiven Code und wird normalerweise von Sprachen wie C und C++ verwendet . Die Subroutine ruft dann die ihr übergebenen Parameter ( srcund dst) vom Stack ab. Dann wird eine Schleife durchlaufen, ein ASCII-Zeichen (ein Byte) aus der srcZeichenfolge gelesen , überprüft, ob es sich um ein alphabetisches Großbuchstaben handelt, und wenn ja, wandelt es in ein Kleinbuchstaben um, ansonsten belässt es es so, wie es ist, und schreibt das Zeichen dann in die dstSaite. Schließlich prüft es, ob das Zeichen ein Nullzeichen war ; wenn nicht, wiederholt es die Schleife, andernfalls stellt es den vorherigen Stapelrahmen (und das A6-Register) wieder her und kehrt zurück. Beachten Sie, dass die Zeichenfolgenzeiger (Register A0 und A1) bei jeder Iteration der Schleife automatisch inkrementiert werden.

Im Gegensatz dazu ist der folgende Code für eine eigenständige Funktion, selbst in der restriktivsten Version von AMS für die TI-89- Rechnerserie, Kernel-unabhängig, ohne dass bei der Ausführung Werte in Tabellen, Dateien oder Bibliotheken nachgeschlagen werden. keine Systemaufrufe, keine Ausnahmeverarbeitung, minimal zu verwendende Register, noch die Notwendigkeit, irgendwelche zu speichern. Es gilt für historische julianischen Daten vom 1. März 1 n. Chr. oder für Gregorianische . In weniger als zwei Dutzend Operationen berechnet es eine mit ISO 8601 kompatible Tagesnummer, wenn es mit drei Eingaben aufgerufen wird, die an den entsprechenden STANDORTEN gespeichert sind:

;

; WDN, an address - for storing result d0

; FLAG, 0 or 2 - to choose between Julian or Gregorian, respectively

; DATE, year0mda - date stamp as binary word&byte&byte in basic ISO-format

;(YEAR, year ~ YEAR=DATE due to big-[[Endianness#Current_architectures|endianness]])

;

move.l DATE,d0

move.l d0,d1

;

; Apply step 1 - [[SuperBASIC#Example|Lachman's congruence]]

andi.l #$f00,d0

divu #100,d0

addi.w #193,d0

andi.l #$ff,d0

divu #100,d0 ; d0 has the month index i in the upper word (mod 100)

;

; Apply step 2 - Using spqr as the Julian year of the leap day preceding DATE

swap d0

andi.l #$ffff,d0

add.b d1,d0

add.w YEAR,d0

subi.l #$300,d1

lsr #2,d1

swap d1

add.w d1,d0 ; spqr/4 + year + i + da}}

;

; (Apply step 0 - Gregorian adjustment)

mulu FLAG,d1

divu #50,d1

mulu #25,d1

lsr #2,d1

add.w d1,d0

add.w FLAG,d0 ; (sp32div16) + spqr/4 + year + i + da

;

divu #7,d0

swap d0 ; d0.w becomes the day number

;

move.w d0,WDN ; returns the day number to address WDN

rts

;

; Days of the week correspond to day numbers of the week as:

; Sun=0 Mon=1 Tue=2 Wed=3 Thu=4 Fri=5 Sat=6

;

Siehe auch

- Motorola 68000-Serie

- Motorola 6800 – ein 8-Bit-Vorgänger

- DTACK Grounded – ein früher 68000 Newsletter

Verweise

Weiterlesen

- Datenblätter und Handbücher

- M68000 Mikroprozessor Bedienungshandbuch (9. Ausgabe) ; Motorola (Freescale); 224 Seiten; 1996.

- Nachtrag zum M68000 Benutzerhandbuch (Rev 0) ; Motorola (Freescale); 26 Seiten; 1997.

- Referenzhandbuch für Programmierer der M68000-Familie ; Motorola (Freescale); 646 Seiten; 1991; ISBN 978-0137232895 .

- Bücher

- 68000, 68010, 68020 Grundierung ; 1. Aufl.; Stan Kelly-Bootle und Bob Fowler; Howard Sams & Co; 370 Seiten; 1985; ISBN 978-0672224058 . (Archiv)

- Den 68000-Mikroprozessor beherrschen ; 1. Aufl.; Phillip Robinson; Registerbücher; 244 Seiten; 1985; ISBN 978-0830608867 . (Archiv)

- Pocket Guide Assembly Language für die Serie 68000 ; 1. Aufl.; Robert Erskine; Pitman-Publishing; 70 Seiten; 1984; ISBN 978-0273021520 . (Archiv)

- Motorola M68000 Die-Schaltpläne [1]

- 68000 Maschinencode-Programmierung (68000, 68008, 68010 und 68020 Prozessoren); 1. Aufl.; David Barrow; Collins Fach- und Fachbücher; 234 Seiten; 1985; ISBN 0-00-383163-9 .

Externe Links

- comp.sys.m68k FAQ

- Beschreibungen der Assembler-Anleitung

- 68000 Bilder und Beschreibungen bei cpu-collection.de

- EASy68K , ein Open-Source 68k-Assembler für Windows

- die 68k- und m88k-Ressource – mit Informationen zu den VME-basierten 68k-Boards von Motorola